An asynchronous counter is really cool because it can handle a total of 2n-1 different counting states. For example a 4-bit counter set up as MOD-16 can count from 0 all the way to 15, making it great for things like frequency division.

But you can also use the basic design of an asynchronous counter to create special counters that count fewer numbers than it could normally handle. This is where modulo or MOD counters come into play.

The way this works is by making the counter reset to zero when it hits a certain number which creates a type of asynchronous counter that has shorter counting sequences. In this case an n-bit counter that counts all the way up to its full range (2n) is called a full sequence counter while one that counts to a smaller number is known as a truncated counter.

You might wonder why someone would make an asynchronous truncated counter that doesnt follow the usual MOD-4, MOD-8, or other powers of two. The answer is that it allows us to use combinational logic which helps us take advantage of the asynchronous inputs on the flip-flop, making the counter design more flexible and useful.

In digital electronics, you can take an asynchronous counter that works with modulo-16 and make it even better by adding some extra logic gates. This change lets the counter act like a decade counter which can count up to ten. This is super helpful for regular decimal counting and in arithmetic circuits.

These special counters are called Decade Counters. One important thing about a decade counter is that it has to reset to zero when it reaches the number ten which in binary is shown as DCBA = 1010.

To make this reset happen, you need to connect this specific condition back to the counter’s reset input.

The counting goes from the binary “0000” (which is BCD = “0”) all the way to “1001” (which is BCD = “9”).

This type of counter is known as a BCD (binary-coded decimal) counter because its ten counting states match the BCD code. However binary decade counters are actually used more often in different applications.

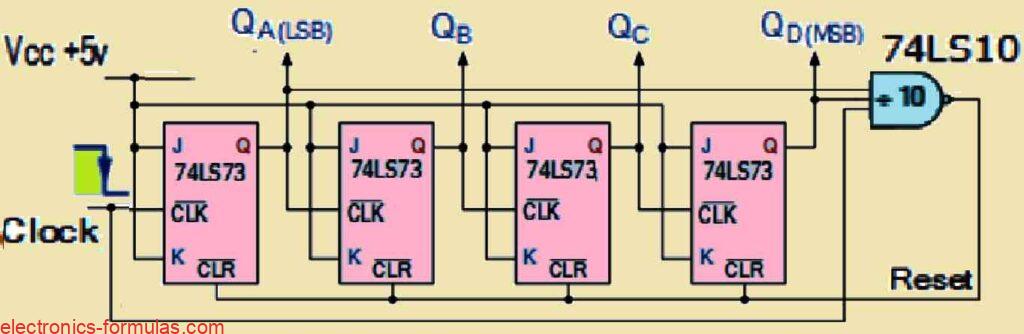

Asynchronous Decade Counter

This type of asynchronous counter is made to increase its count every time the input clock signal goes from high to low, starting at 0000 in binary and counting up to 1001 which is the decimal number 9.

At this point, the outputs labeled QA and QD both show a logic “1.” When the next clock pulse comes, the output from the 74LS10 NAND gate changes from a logic “1” to a logic “0.”

Since the output from the NAND gate is connected to the CLEAR (CLR) inputs of all the 74LS73 J-K Flip-flops, this signal resets all Q outputs back to 0000 when the count hits 10.

As a result both QA and QD go back to a logic “0” after the flip-flops reset, and the NAND gate output goes back to a logic “1.”

This starts a new counting cycle for the counter, which begins again from 0000. This setup creates a decade or Modulo-10 up-counter.

Truth Table for Decade Counter

| Clock Count | Output bit Pattern | Decimal Value | |||

| QD | QC | QB | QA | ||

| 1 | 0 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 0 | 1 | 1 |

| 3 | 0 | 0 | 1 | 0 | 2 |

| 4 | 0 | 0 | 1 | 1 | 3 |

| 5 | 0 | 1 | 0 | 0 | 4 |

| 6 | 0 | 1 | 0 | 1 | 5 |

| 7 | 0 | 1 | 1 | 0 | 6 |

| 8 | 0 | 1 | 1 | 1 | 7 |

| 9 | 1 | 0 | 0 | 0 | 8 |

| 10 | 1 | 0 | 0 | 1 | 9 |

| 11 | Outputs are reset to zero by the counter. | ||||

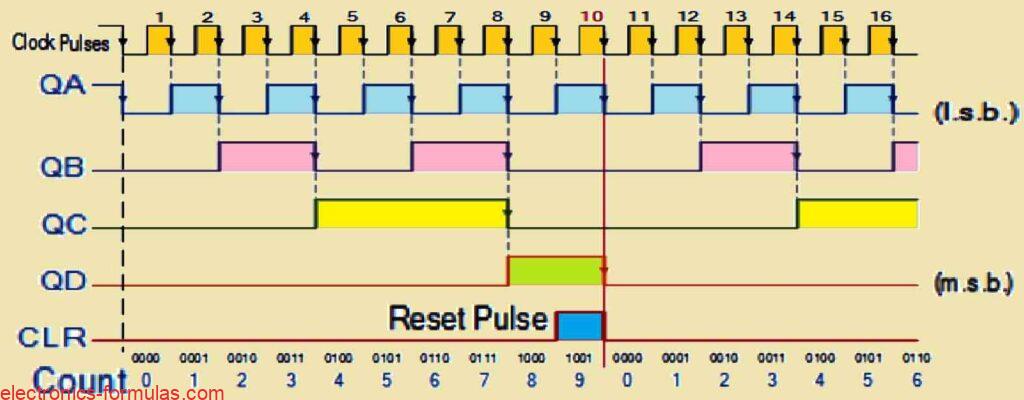

Timing Diagram for the Decade Counter

The circuit indicated can be easily changed to work with different counting cycles by using the same idea of cutting off the output sequences from the counter. You can do this by simply changing the connections to the inputs of the NAND gate or by using different types of logic gates.

For example if you want to make a counter that goes up to twelve, or a modulo-12 counter then you can do this easily by connecting the inputs of the NAND gate to the outputs called “QC” and “QD.”

It’s also good to know that the binary form of the number 12 is 1100 and the output “QA” is the least significant bit (LSB).

When designing truncated asynchronous counters, its important to realize that the highest count you can get with n flip-flops is 2 raised to the power of n.

So when you start designing these counters then you need to find the smallest power of two that is equal to or greater than the count you want.

For instance if you want to count from 0 to 39 which means you need a mod-40 counter, then you will need six flip-flops or n = 6. This setup gives you a maximum count of 64 because if you only use five flip-flops then you would only be able to count up to 32.

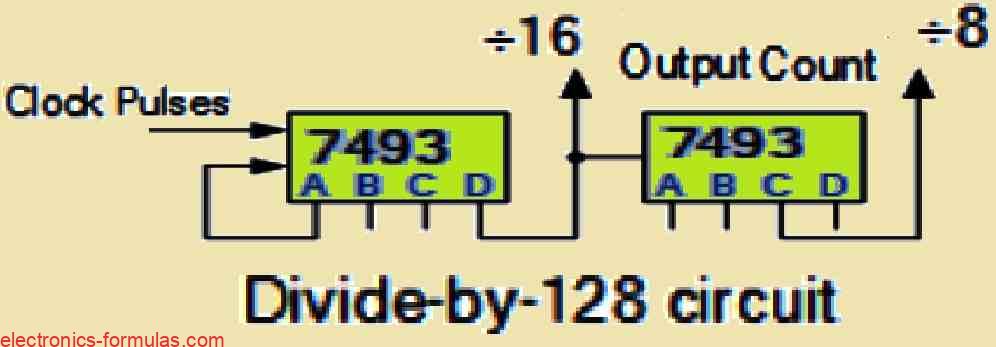

Now, to build a counter that divides a frequency by 128, we need to use seven flip-flops because 128 is equal to 2 raised to the 7th power. If we decide to use dual flip-flops like the 74LS74 then we will still need four integrated circuits to complete the circuit assembly.

Cascading Two TTL 7493

A simple way to approach this is by using two TTL 7493 integrated circuits which act as 4-bit ripple counters or dividers.

Since 128 can be broken down into 16 times 8, you can set one of the 7493 chips to divide by 16 and the other to divide by 8.

By connecting these two circuits together you can create a frequency divider that works at a division factor of 128, as shown in the following diagram.

Besides this method there are also standard integrated circuit asynchronous counters available, like the TTL 74LS90 programmable ripple counter/divider.

This IC can be set up to divide by 2, divide by 5, or any mix of those. Additionally the 74LS390 is a very flexible dual decade driver integrated circuit that provides many division options, including divide-by-2, 4, 5, 10, 20, 25, 50, and 100.

“divide-by-n” Frequency Division Feature

The cool thing about ripple counters is that they can shorten sequences to create a “divide-by-n” output.

This means that ripple counters can work really well as frequency dividers. They help change a high clock frequency into a lower one which is super useful for things like digital clocks and timing devices.

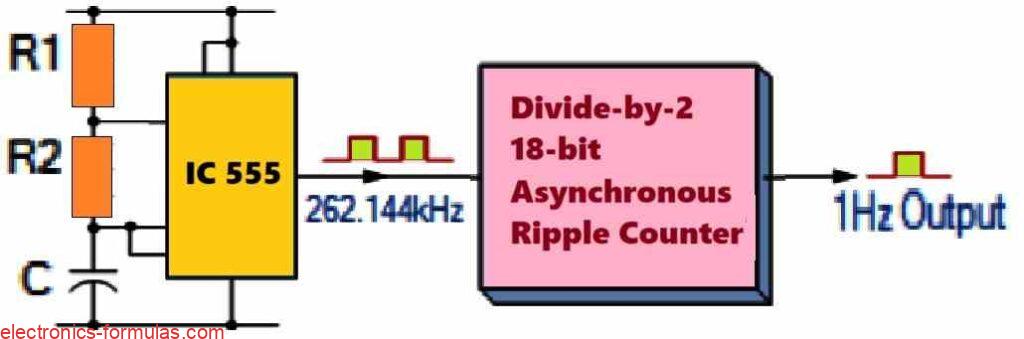

For example if we need a precise 1Hz timing signal for a digital clock then we can use a regular 555 timer chip set up in Astable Multivibrator mode to make a 1Hz square wave signal.

But we should keep in mind that the 555 timer usually has a timing error of about 1% to 2% depending on the brand. At such a low frequency like 1Hz, a 2% error can cause some serious issues.

The data sheet of the IC gives us important details showing that the 555 timer can work at a top frequency of about 300kHz.

At this high frequency, theres a 2% error margin which is a bit high but still okay when the frequency is lower, like around 6kHz. If we choose a higher timing frequency like 262.144kHz, along with an 18-bit ripple (Modulo-18) counter then we can create a very accurate timing signal of 1Hz, as explained in the following section.

Using 18-bit Asynchronous Ripple Counter to Generate 1Hz Timing

This example although is quite simple, it helps explain the basic ideas behind creating accurate timing frequencies. By using high-frequency crystal oscillators along with multi-bit frequency dividers, we can make precise frequency generators that are useful in many different areas.

These can be found in everyday items like clocks and watches, as well as in more complicated devices like event timers, electronic pianos, synthesizers, and other musical tools.

However there is a notable issue with asynchronous counters. There is a small delay that happens between when a clock pulse hits the input and when it shows up at the output. This delay is caused by the internal parts of the gate.

In asynchronous circuits, this delay is known as Propagation Delay which is why people sometimes call the asynchronous ripple counter a “propagation counter.”

When dealing with the high frequencies this delay can cause mistakes in the output counts.

Additionally in large bit ripple counter setups, the delays from each stage can add up resulting in a significant total delay by the time the counting is finished.

This means that the timing difference between the input signal and the counted output signal can become quite noticeable.

Because of this, the asynchronous counters are usually not used in high-frequency counting situations, especially when there are many bits involved.

The outputs from the counter do not happen at the same time, instead they occur at different moments.

This happens because of the order in which they are activated. It is kind of like a line of dominoes falling one after the other.

So when you add more flip-flops to an asynchronous counter then the highest speed it can work at actually goes down.

This is important to keep the counting accurate. To deal with the delays that can happen, the engineers created Synchronous Counters as a better option.

Advantages of Asynchronous Counters

Here are some cool things about Asynchronous Counters:

- You can easily build them using Toggle or D-type flip-flops.

- They are called “Asynchronous Counters” because not all the flip-flops are triggered by the same clock signal.

- Each output depends on the change from the previous flip-flop’s output.

- People often call them ripple counters because the data seems to “ripple” from one flip-flop to the next.

- They work well in “divide-by-n” counter circuits.

- Truncated counters can count to any modulus number you want.

Disadvantages of Asynchronous Counters

- Asynchronous Counters have some important downsides that we should think about.

- First you might need an extra flip-flop just for “re-synchronization.”

- Also if you want to count a sequence that doesn’t fit the usual 2n pattern then you will need to add some extra feedback logic.

- Plus when you are working with a lot of bits, the delay that builds up through each stage can get really high which is why people often call these counters “Propagation Counters.”

- It is also worth mentioning that counting mistakes can happen when the clock speed is really fast.

- On the other hand Synchronous Counters are a better choice because they are faster and more reliable since they use the same clock signal for all the flip-flops.

References:

What is an asynchronous counter?

Why asynchronous counters can not work at high clock frequencies?

Leave a Reply